# ELEX 7660 Now You See Me Project Report

Ken Do, Andrew Obermeyer 4-14-2017

# Contents

| 1 - Overview                        | 3  |

|-------------------------------------|----|

| 1.1 - Project Motivation            | 3  |

| 1.2 - Goals                         | 3  |

| 1.3 - System Block Diagram          | 3  |

| 1.4 - IP and Hardware Descriptions  | 4  |

| 2 - Outcome                         | 5  |

| 2.1 - Results and Successes         | 5  |

| 2.2 - Design Reviews                | 5  |

| 2.3 - Possibilities for Future Work | 5  |

| 3 - Description of Design Blocks    | 6  |

| 3.1 - Infrared Sensors              | 6  |

| 3.2 – Photo-resistor and ADC        | 7  |

| 3.3 - Timer Algorithm               | 8  |

| 3.4 - Street Light Circuit Model    | 9  |

| 4 - Systemverilog Code1             | .2 |

| 4.1 - ADC.sv Module1                | .2 |

| 4.2 - top.sv Module1                | .7 |

# Table of Figures

| Figure 1: System Block Diagram                                                                                                                                                                                                                                                                   | 3  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 2: Infrared light can't be seen with the naked eye but can be as purple light with your phone's camera. This image was taken while cycling through the IR emitter/receiver pairs                                                                                                          | 6  |

| Figure 3: Infrared emitter LEDs (clear) directed at the infrared light detectors (black)                                                                                                                                                                                                         | .7 |

| Figure 4: Photo-resistor circuit.                                                                                                                                                                                                                                                                | 8  |

| Figure 5: States of the scount[i] signal                                                                                                                                                                                                                                                         | 9  |

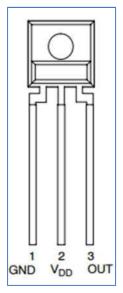

| Figure 6: The TSL267 side-looker infrared receiver.                                                                                                                                                                                                                                              | 10 |

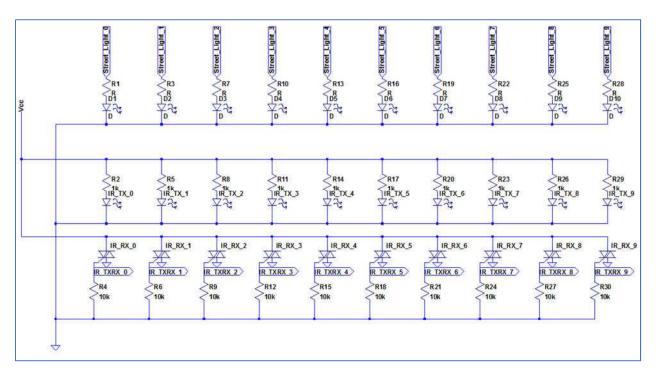

| Figure 7: Circuit diagram of the model street light system.                                                                                                                                                                                                                                      | 10 |

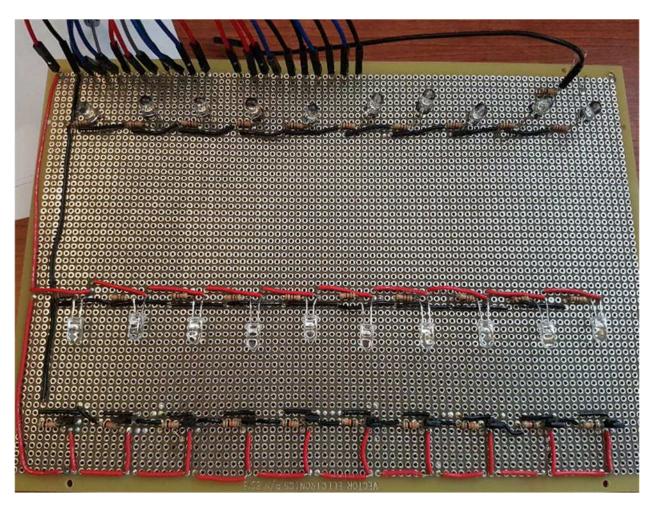

| Figure 8: As-built model of the street light system containing rows of Street lights (top), IR emitter (middle), and IR receiver (bottom). Vcc are the red wires, common are the black wires. Photo-resistor circuit located on top right. FPGA connections are the row of wires on the top left |    |

## 1 - Overview

### 1.1 - Project Motivation

Our street lighting requirements consume the largest amount of energy in our road infrastructure. The transition to more efficient light technology such as LED fixtures have improved the situation, but further reduction of energy consumption can only be realized by improving the lighting control systems.

The current control scheme turns on the lights at a set time or ambient light level. Once the set point is reached, the fixtures remain on at 100% output throughout the night. In locations with minimal to no traffic, these fixtures are consuming energy with no purpose. It is equivalent to leaving a light on in a vacant room overnight.

### 1.2 - Goals

Extending the lighting control systems ability to detect traffic will allow the system to provide sufficient light output when needed, and return to a low energy state once traffic has cleared. This is achieved by implementing the following system components:

- Use the FPGA's ADC to determine the output from a photo-resistor which will determine the amount of ambient light and trigger the device to enter night mode or day mode.

- Use the output from infrared sensors to detect motion on different sections of the modelled street. This could be accomplished using the ADC, external comparators, or directly using the outputs from the sensors as signals, if the voltage levels are consistent with logic levels.

- When at night and motion (a passing car) has been detected, turn on street lights where the car currently is as well as lights ahead of its path.

- Automatically turn off these lights once the car has passed, by creating timers on the FPGA.

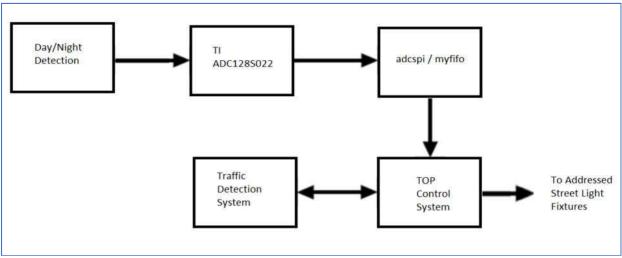

### 1.3 - System Block Diagram

Figure 1: System Block Diagram.

# 1.4 - IP and Hardware Descriptions

| Hardware / IP                                | Core Function                                                                                                                                                                                                 | <u>Creator(s)</u>       |

|----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|

| CDS<br>Photoconductive<br>Photocell          | <ul> <li>Photocell designed to sense light from 400 to 700 nm.</li> <li>Dark resistance = 500 kΩ</li> <li>Illuminated resistance = 33 kΩ</li> </ul>                                                           | Luna<br>Optoelectronics |

| Day/Night Detection<br>System                | <ul> <li>Simple resistor divider circuit containing a photocell.</li> <li>Voltage output at the center of the resistor divider varies due to changes in light intensity detected by the photocell.</li> </ul> | Andrew, Ken             |

| TI ADC128S022                                | <ul> <li>Built-in ADC module used to read Day/Night<br/>Detection voltage output levels.</li> </ul>                                                                                                           | Texas<br>Instruments    |

| Adcspi                                       | <ul> <li>Interfaces with the serial output of the built-in<br/>ADC module on the FPGA and stores the<br/>quantized data from channels 0 and 1.</li> </ul>                                                     | Ed Casas                |

| myfifo                                       | • "First In First Out" interface to with adcspi.                                                                                                                                                              | Ken, Andrew             |

| IR Emitter<br>(LTR-4206E)                    | <ul> <li>Emits Infrared light with a wavelength of 940 nm</li> </ul>                                                                                                                                          | LITEON                  |

| IR Light to Voltage<br>Converter<br>(TLS267) | <ul> <li>Converts 940nm IR light intensity to output voltage</li> </ul>                                                                                                                                       | TAOS                    |

| Traffic Detection<br>System                  | <ul> <li>Reads the voltage output from the IR detector<br/>associated to a street light location to detect<br/>traffic.</li> </ul>                                                                            | Andrew, Ken             |

| Top Control System                           | <ul> <li>Sets street light output levels according to<br/>information provided by Day/Night and Traffic<br/>detection systems.</li> </ul>                                                                     | Ken, Andrew             |

# 2 - Outcome

### 2.1 - Results and Successes

The Day/Night detection system used a simple resistor divider circuit containing the photocell and was successful in detecting ambient lighting levels. The ADC quantization provided sufficient information to allow the programmer to set desired thresholds to distinguish between day and night scenarios.

The traffic detection system used the IR emitter/receiver pair to detect traffic. Each IR pair was addressed to match the light fixture location. The voltage output of the IR receiver provided a digital signal to the Top Control system. When sufficient IR light is detected, a high digital logic signal is sent to the Top Control system.

The Top Control system used the information provided by the previous two systems to control street light output. During day mode, all the street lights are deactivated. When night mode is detected, the street light output is determined by the traffic detection system. The traffic detection and the Timer algorithm within the Top Control system allowed for an active street lighting control system. When traffic is detected, the fixture in that location and the two sections ahead of that location are activated. This system successfully reduced the energy consumption of the street lights by only providing sufficient street lighting output when needed.

The Timer algorithm ensured the correct street lights were activated for a sufficient amount of time. The timer allowed for the street lights to remain active for a set period after traffic has cleared in that location. The traffic in that area will observe adequate lighting on the road ahead and behind them. The development of the timer algorithm within Quartus provided challenges due to Quartus not generating the expected hardware. Drawing out the state diagram helped produce the simplest code, which then generated the required hardware.

### 2.2 - Design Reviews

Our original plan was to use the ADC to determine the output level from the IR receivers, as initial testing determined that the 'blocked' and 'unblocked' voltages were approximately 0.6V and 1V respectively. We designed the system based on using one ADC channel to measure all 10 IR receivers, by only turning one transmitter/receiver pair on at a time and syncing this with the ADC conversion time. This was based on the incorrect assumption that the receiver outputs were high impedance. When this didn't work, we tested the receiver outputs with a higher intensity IR from the transmitters, and determined that the 'blocked' and 'unblocked' output voltages were 0.3V and 3.2V respectively, when using the FPGA's Vcc of 3.3V. This is sufficient for logic levels, and when combined with having all of the transmitters and sensors on 100% of the time rather than cycling through them, was used directly as the signal for the zone being tripped.

### 2.3 - Possibilities for Future Work

The model designed in this project serves as a basis for future expansion of features of a smart street light control system. Different scenarios could be implemented based on where the section of road is located. If the road is in a remote area, the auto-off system would be ideal as there would be limited vehicle traffic and no pedestrian traffic at night. In a more highly populated area, it might be more practical to have the lights dimmed rather than completely turned off when there is no traffic. This could simply be done using pulse-width modulation.

As stated previously, we attempted to use the ADC to measure the IR intensity at the receiver. Using the ADC would likely be the best way to implement this, as you could use any kind of IR sensor. This would require either using more ADC channels, or a means of isolating individual sensors.

The system as-built only supports one-way traffic, due to the way the timer module was designed to turn on the next two lights when a sensor is tripped. Upgrading to bi-directional movement would be possible with using an extra sensor at either end of the road segment to determine the direction of a moving vehicle.

# 3 - Description of Design Blocks

### 3.1 - Infrared Sensors

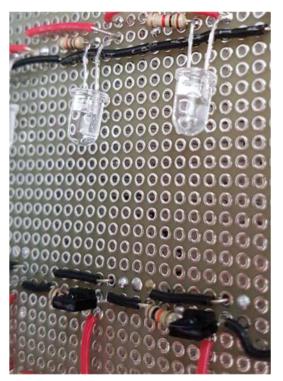

Infrared light sensors are commonly used for motion detection. While some, such as the yard light sensors found on many houses, are sensitive enough to pick up the infrared given off as body heat, others use a transmitter and receiver to create a stronger beam of infrared light whose intensity is determined by the receiver. This setup is commonly used as the safety sensor for automatic garage doors, to stop the door from closing if something or someone gets in the way, similar to Figure 3. We will use this technology as the motion sensors for our street light control system.

*Figure 2: Infrared light can't be seen with the naked eye but can be as purple light with your phone's camera. This image was taken while cycling through the IR emitter/receiver pairs.*

### Project Report: Now You See Me

Ken Do Andrew Obermeyer April 14, 2017

Figure 3: Infrared emitter LEDs (clear) directed at the infrared light detectors (black).

The IR sensors 'blocked' and 'unblocked' output voltages are approximately 0.3V and 3.2V respectively, when using the FPGA's Vcc of 3.3V. These voltage levels are sufficient for high and low logic levels, and are used as signals to directly drive the IR\_LED\_TxRx\_Enable[i] signals for the light timer algorithm.

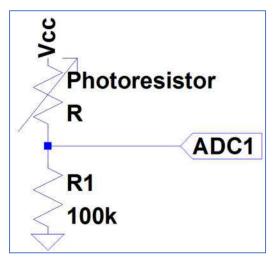

### 3.2 – Photo-resistor and ADC

The simple photo-resistor circuit shown in Figure 4 is widely used to detect ambient lighting levels due to its simplicity. The light intensity detected by the photocell changes its resistance. This allows the output voltage to vary with changes in light level intensity.

Using the built-in ADC on the FPGA board allowed for adjusting day/night detection threshold. The adjustability of this parameter enables this system to meet the requirements of different locations.

The ADC chip on the FPGA board was interfaced with the "adcspi.sv" module developed by Ed Casas. This module provides the ADC chip with signals for chip select, SCLK, and data in. It also receives the data out from the ADC. This module is configured to read ADC values from channels 0 and 1 on the ADC chip. Both values are stored as "data" register in the "adcspi.sv" module. Interfacing "myfifo.sv" module with "adcspi.sv" ensured that the first data conversion in was the first data conversion out.

*Figure 4: Photo-resistor circuit.*

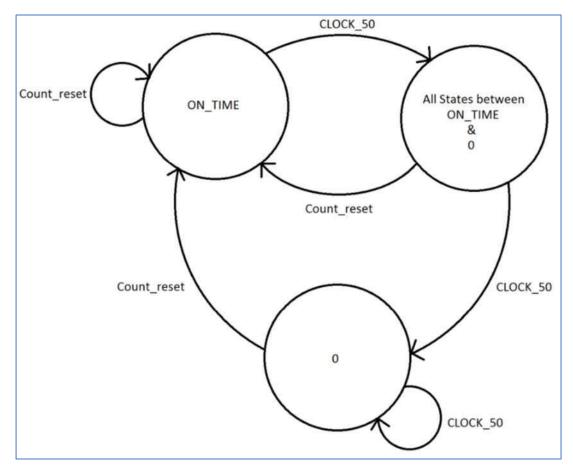

### 3.3 - Timer Algorithm

The auto-off timer control block is used to turn off individual street lights after they have they have been turned on by the IR\_LED\_TxRx\_Enable[i] from the infrared receivers. The lights themselves are turned on by the scount[i] signal being greater than 0.

The timer algorithm can be visualized by the state transition diagram for the scount[i] signal below in Figure 5. Whenever a sensor is tripped, the value of ON\_TIME (150,000,000 clock cycles, which is approximately 3 seconds), is loaded into scount[i] for the corresponding street light that is to be turned on. Because we wish to light the path ahead of the moving vehicle, the code also resets scount[i] for the next two street lights in series. The value of scount[i] is decremented every clock cycle, until it reaches 0, in which case it stays there. At any time, the value of scount[i] can be reset back to the value of ON\_TIME, thus resetting the counter if the corresponding sensor or one of the previous two sensors are tripped.

The timer control block will only run if the operating mode is set to AUTO\_OFF.

Figure 5: States of the scount[i] signal.

### 3.4 - Street Light Circuit Model

The street lights, modelled as a row of LEDs, are individually powered by the output signals Street\_Light[i]. They use a  $1k\Omega$  resistor to control the current. The IR transmitter LEDs also use a  $1k\Omega$  resistor to limit current, but are all powered by the 3.3V Vcc of the FPGA. Both of these sets of LEDs are wired to common rails and connected to common on the FPGA. The IR receivers, Figure 6, are a 3-pin device, requiring Vcc and common from the FPGA. There is a  $10k\Omega$  resistor from output to common, and the output pin is also directly connected to the IR\_LED\_TxRx\_Enable[i] input signal to the FPGA.

Figure 6: The TSL267 sidelooker infrared receiver.

*Figure 7: Circuit diagram of the model street light system.*

Figure 8: As-built model of the street light system containing rows of Street lights (top), IR emitter (middle), and IR receiver (bottom). V<sub>cc</sub> are the red wires, common are the black wires. Photo-resistor circuit located on top right. FPGA connections are the row of wires on the top left.

# 4 - Systemverilog Code

4.1 - ADC.sv Module

```

// ADC.sv module - This module interfaces with the ADC of the FPGA board.

The ADC is used to detect day time status using a photocell.

11

// Modified by: Ken Do, Andrew Obermeyer

// Date: April 9, 2017

`define MAXIRPAIR 9 // the largest address for IR pairs

`define CLOCK DIV 10000 // Divisor for the ADC clock

`define THRESHOLD 300 // LED comparison threshold

module ADC

(

input logic CLOCK 50,

// reset_n

input logic [1:0] KEY,

output logic [3:0] IRPAIR, // selects IR pair to be sampled.

// GATE indicates the traffic status on the road. Bits 0 - MAXIRPAIR

// represent the status of the IR sensors. Bit MAXIRPAIR + 1

// represents the PHOTOCELL status.

output logic [(`MAXIRPAIR+1):0] GATE,

// ADC SPI interface

output logic ADC_CS_N, // ssn

output logic ADC_SADDR, // mosi

output logic ADC SCLK, // sclk

input logic ADC SDAT // miso

);

logic ready, valid, oready, ovalid;

logic [31:0] data, odata;

logic reset n, clk;

assign reset n = KEY[0];

// Divide module input clock by CLOCK DIV.

logic [31:0] count;

always ff @ (posedge CLOCK 50) begin

if (count <= 0) begin</pre>

count <= `CLOCK DIV;</pre>

clk <= ~clk;</pre>

end

else count <= count - 1'b1;</pre>

end

adcspi a0

(

.sclk(ADC_SCLK), // output to ADC clock

.mosi(ADC_SADDR), // output to ADC DIN (address)

.ssn(ADC_CS_N), // output to ADC chip select

.miso(ADC_SDAT), // input from ADC (DATA)

```

```

.ready(ready),

// input

.valid(valid),

// output

// the ADC conversion data

.data(data),

.clk(clk), .reset(~reset n)

);

// Photocell data control and output status.

myfifo fifo0

(

.ready (ready),

.valid(valid),

.data(data),

.oready (oready),

.ovalid(ovalid),

.odata(odata),

.IRPAIR(IRPAIR), // OUTPUT TO SYNCHRONIZE IR PAIR WITH ADC DATA

.reset (reset n),

.clk(clk)

);

assign oready = '1;

logic [11:0] PHOTOCELL, TRAFFIC;

assign PHOTOCELL = data[27:16];

assign TRAFFIC = data[15:0];

always ff @(posedge clk)

GATE [10] = (IRPAIR != 9) ? GATE [10] : (PHOTOCELL < 3000) ? 1'b1 : 1'b0;

endmodule

// -- start of adcspi.sv ---

// SPI master interface for TI ADC128S022

// for ELEX 7660 201710 Lab 5

// Ed.Casas 2017-2-16

// reads channels 0 and 1

// sclk is clk is divided by 16

// output is 16-bit samples from channels 0 and 1

// samples packed into 32 bits (ch 0 in MS byte)

// ADC128S0022 interface:

// 16 bit transfers

// mosi and cs* change on falling edge of sclk

// mosi bits 13:11 are (next) channel number

// miso sampled on rising edge of sclk

// miso data is on ls 12 bits of miso

// sample rate is sclk rate / 16

```

```

// sample rate must be 50 to 200 kHz

// sclk rate must be 800 kHz to 3.2 MHz

// e.g. 50 MHz / 32 = 1.5625 MHz sclk, ~98kHz sampling

// mosi timing relative to rising edge of sclk:

// setup is >10ns, hold >10ns

// miso timing is relative to falling edge of sclk:

// access is <27ns, hold ~4ns</pre>

module adcspi

(

output logic sclk, mosi, ssn, // SPI master

input logic miso,

input logic ready, // ready/valid data out

output logic valid,

output logic [31:0] data,

input logic clk, reset

);

parameter MISO = {5'b00001,27'b0} ;

// clock/bit counter

struct packed {

logic wordcnt ;

logic [3:0] bitcnt ;

logic sclk ;

logic [3:0] clkcnt ; } cnt, cnt_next ;

logic [31:0] sr ;

// shift register

logic rising, falling, done ;

assign sclk = cnt.sclk ;

// done all bits

assign done = cnt ==? '{'1, '1, '1, '1};

// clock/bit counter

assign cnt next = ( reset || done ) ? '0 : cnt+1'b1 ;

always@(posedge clk)

cnt <= cnt next ;</pre>

assign rising = cnt next.sclk && ~cnt.sclk ;

assign falling = ~cnt next.sclk && cnt.sclk ;

always@(posedge clk) begin

// shift mosi out

if ( falling )

mosi <= sr[31] ;

// shift miso in

if ( rising )

sr <= {sr[30:0],miso} ;</pre>

```

```

// channel select serial out

mosi <= MISO[31] ;

valid <= '1 ;

// data ready

end

if ( ready && valid ) // data was read

valid <= '0 ;

end

always@(posedge clk) // run continously

ssn <= reset ;</pre>

endmodule

// myfifo.sv - FIFO with ready/valid input and output

// for ELEX 7660 201710 lab 5

// Created by: Ed Casas

// Modified by: Ken Do, A

Ken Do, Andrew Obermeyer

module myfifo

(

output logic ready, // ready/valid input

input logic valid,

input logic [31:0] data,

input logic oready, // Avalon-ST output

output logic ovalid,

output logic [31:0] odata,

output logic [3:0] IRPAIR,

input logic reset, clk

);

parameter W = 3;

parameter N = 8;

// Dual-ported RAM

logic [31:0] DPRAM [7:0];

logic [2:0] readp, readp next, writep, writep next; // DPRAM in/out

pointers

always ff @(posedge clk) begin

if (reset) begin

readp <= 3'b0;

writep <= 3'b0;

IRPAIR \leq 4'b0;

end

```

```

if (ready) begin

DPRAM[writep] <= data;</pre>

if (IRPAIR >= 0 || IRPAIR < `MAXIRPAIR)

IRPAIR <= IRPAIR + 1'b1;</pre>

else

IRPAIR <= 4'b0;</pre>

end

if (valid)

writep <= writep_next;</pre>

if (ovalid && oready)

readp <= readp next;</pre>

end

// combinational logic for RAM status

always comb begin

// input combinational logic

ready = ((writep + 1'b1) != readp) ? 1'b1 : 1'b0;

writep next = (valid && ready) ? (writep + 1'b1) : writep;

// output combinational logic

ovalid = (readp != writep) ? 1'b1 : 1'b0;

readp next = (oready && ovalid) ? (readp + 1'b1) : readp;

odata = DPRAM[readp];

end

endmodule

```

```

4.2 - top.sv Module

```

```

// BCIT ELEX 7660 Final Project - Now You See Me

// Ken Do & Andrew Obermeyer

model

`define DAY_MODE 0 // Day mode: all lights off

`define ALWAYS_ON 1 // Night mode: all lights always on full

intensity

`define AUTO_OFF 2 // Night mode: power saving, (auto) lights off

when no traffic

`define AUTO DIM 3 // Night mode: power saving, (auto) lights dim

when no traffic

`define ON TIME 32'd150000000  // 3 seconds (3 x 50MHz clock) = on time

for street lights when tripped

module top (input logic CLOCK 50,

// System clock

input logic [1:0] KEY,

// Reset signal for ADC

// ADC chip select (active

output logic ADC CS N,

low)

output logic ADC_SCLK,// ADC clock signaloutput logic ADC_SADDR,// ADC control signal outinput logic ADC_SDAT,// ADC miso

input logic [`LED COUNT - 1:0] IR LED TxRx Enable , // Input

from IR recievers

output logic Street Light [`LED COUNT - 1:0], // Output to

individual street lights

output logic [7:0] LED // on board LED's for testing

);

logic [3:0] IRPAIR ; // Input signal from ADC module to turn on

selected IR Transmitter/Reciever Pair

logic [11:0] Lumen_Sensor; // Lumen sensor result from 12-bit ADC

from lumen sensor

logic [11:0] ADC Result; // Result of ADC conversion

logic Street Light Mode Enable [`LED COUNT - 1:0]; // Street-Light

enable signal from mode selector block

logic gate [`LED COUNT - 1:0]; // IR beam broken (motion detected)

tracker

logic [`LED COUNT:0] GATE; // Beam broken signal from ADC module

(bits 0 to 9) Night sensor (bit 10)

// Please note that GATE[9:0] originally was intended to use the ADC to

determine whether the sensors were tripped

```

```

// This was changed due to technical difficulties, and only GATE[10] was

used (for the photoresistor).

logic [1:0] Operating_Mode; // System operating mode:

day/night/power saving

logic [31:0] scount [`LED COUNT - 1:0]; // Counters for each light to

turn off

logic count reset [`LED COUNT - 1:0]; // Count reset signal for timer

block

ADC a1 (.*);

// Instantiate ADC module

// Night/Day selector: change the night mode to one of 3 options based on

desired

// operating preferences. See defines above for details.

always comb begin

if (GATE[10]) begin // GATE[10] is ADC result from ADC module

for the photoresistor

Operating Mode = `AUTO OFF; // Adjust this for operating mode

LED[7] = 1; // Turn on on-board LED #7 for verification

end

else begin

Operating Mode = `DAY MODE;

LED[7] = 0;

end

end

// On-board LED's #0-6 for IR sensor verification

assign LED[0] = ~IR LED TxRx Enable[0];

assign LED[1] = ~IR LED TxRx Enable[1];

assign LED[2] = ~IR LED TxRx Enable[2];

assign LED[3] = ~IR LED TxRx Enable[3];

assign LED[4] = ~IR LED TxRx Enable[4];

assign LED[5] = ~IR LED TxRx Enable[5];

assign LED[6] = ~IR LED TxRx Enable[6];

// Operating mode selector

always comb begin

unique case(Operating Mode)

`DAY MODE: begin // Day mode - disable lights

Street Light Mode Enable[`LED COUNT-1:0] = '{10{'0}};

end

`ALWAYS ON: begin

// Night mode - enable all lights at full power

Street Light Mode Enable[`LED COUNT-1:0] = '{10{1'b1}};

end

`AUTO OFF: begin // Power saving mode (auto off when no motion

detected)

Street Light Mode Enable[`LED COUNT-1:0] = '{10{1'b1}};

end

// Power saving mode (auto dim when no motion

`AUTO DIM: begin

detected) (not implemented)

Street Light Mode Enable[`LED COUNT-1:0] = '{10{1'b1}};

end

endcase

```

```

end

// Auto-off timer control block

always ff @ (posedge CLOCK 50) begin

if(Operating Mode == `AUTO OFF) begin // Only use if this mode

is enabled

for(int i = 0; i < `LED COUNT; i = i + 1) begin // Generate hardware</pre>

for each light

gate[i] <= ~IR LED TxRx Enable[i]; // When a gate is</pre>

tripped, latch the signal

if(gate[i]) begin

// If a gate has been tripped

and latched:

count reset[i] <= 1;

// Signal the count reset

count_reset[1] <= 1;

for the light and the next 2 in series

if(i < ) UPD count 1)</pre>

if(i < `LED COUNT-1)</pre>

// Stop generating hardware

if at the end of the road segment

count reset[i + 1] <= 1;

if(i < `LED COUNT-2)</pre>

count reset [i+2] <= 1;</pre>

// Reset the gate-tripped latch

gate[i] <= 0;

end

// Reset counter to starting position when gate is tripped, or count

down if count has been reset

if(count reset[i]) begin

scount[i] <= `ON TIME;</pre>

count_reset[i] <= 0; // Reset the count_reset signal</pre>

every time beam is triggered

end

else if(scount[i] > 0) // Otherwise keep counting down if

count is not finished

scount[i] <= scount[i] - 1;</pre>

else

scount[i] <= 0; // Stay at 0 if count is finished</pre>

end

end

end

// Final enable signal to LED street lights. Must be enabled by both the

night/day sensor and the counters.

// Signal from street light timers is the scount[i] signal. Lights will

only be on when this counter > 0.

always comb begin

for(int i = 0; i < `LED COUNT; i = i + 1)</pre>

Street Light[i] = (scount[i] > 0) & Street Light Mode Enable[i];

end

endmodule

```